# From CMOS to CMORE: innovation on a MEMS platform

Presenter: Jo De Boeck, Senior VP and CTO imec international

Rudi Cartuyvels, Stephane Donnay, Haris Osman, Ingrid Dewolf, Paru Desphande, Peter Peumans,

imec CMORE-Technology and Lifescience Technology teams

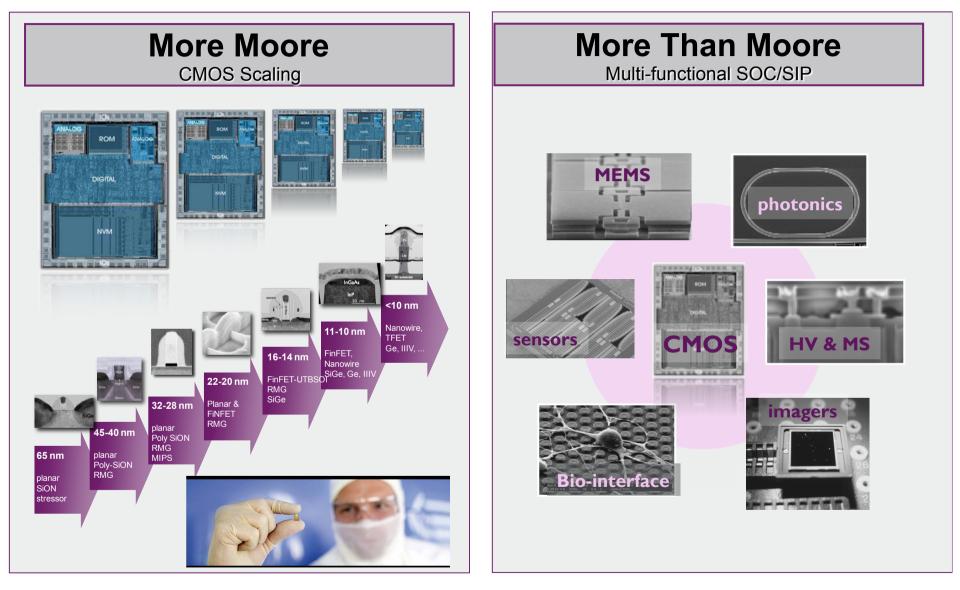

# FROM CMOS TO 'CMORE'

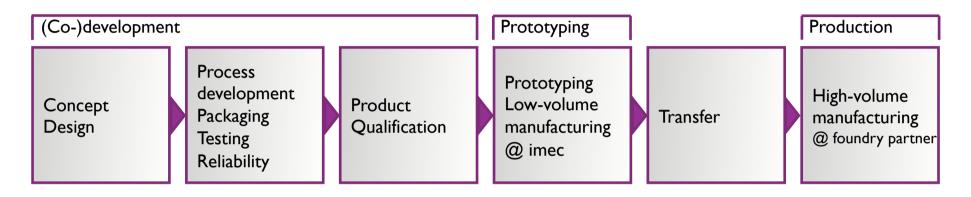

### **CMORE** THE ROUTE FROM SILICON CONCEPT TO A PRODUCT

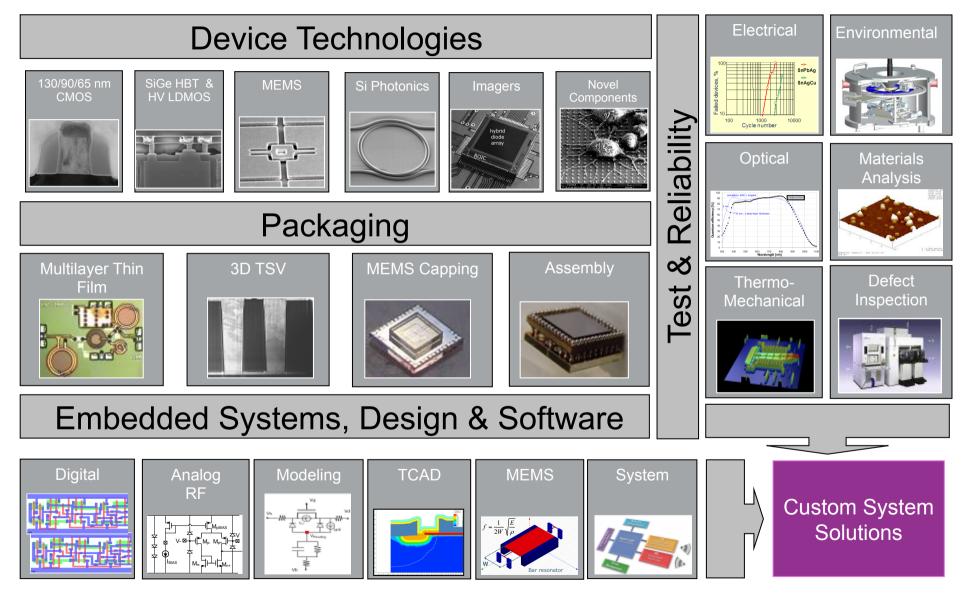

## **CMORE TECHNOLOGY PLATFORMS**

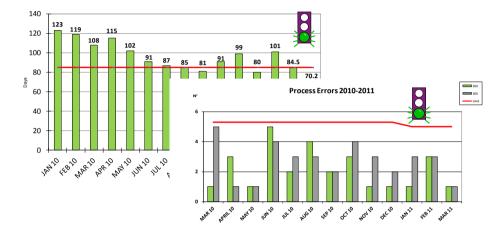

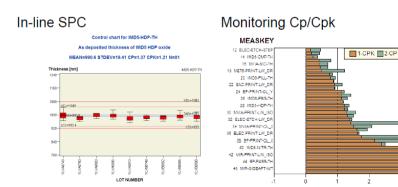

#### **Quality and cycle time KPIs**

#### **Statistical Process Control**

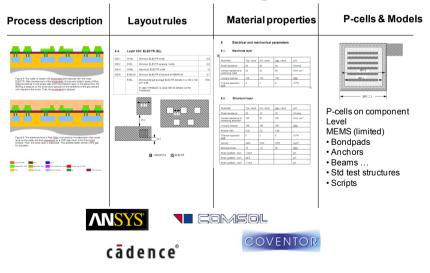

#### Mature design kits

#### imec

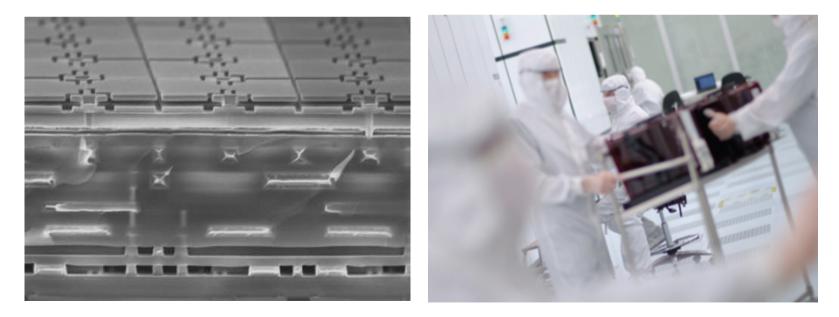

#### IMEC PRODUCES HIGH-QUALITY EUV SENSORS FOR ASML'S NEXT-GENERATION LITHOGRAPHY TOOLS

3 EUV sensors with superior lifetime and sensitivity

high and direct EUV irradiation doses

**CMORE landmark achievement in 2011:** First qualified **CMORE** chipset installed in customer's product

2 EUV position sensors to calibrate, align and focus lens systems

ASML

EUV Energy sensor to monitor EUV dose

imec

# **MEMSTECHNOLOGY VISION**

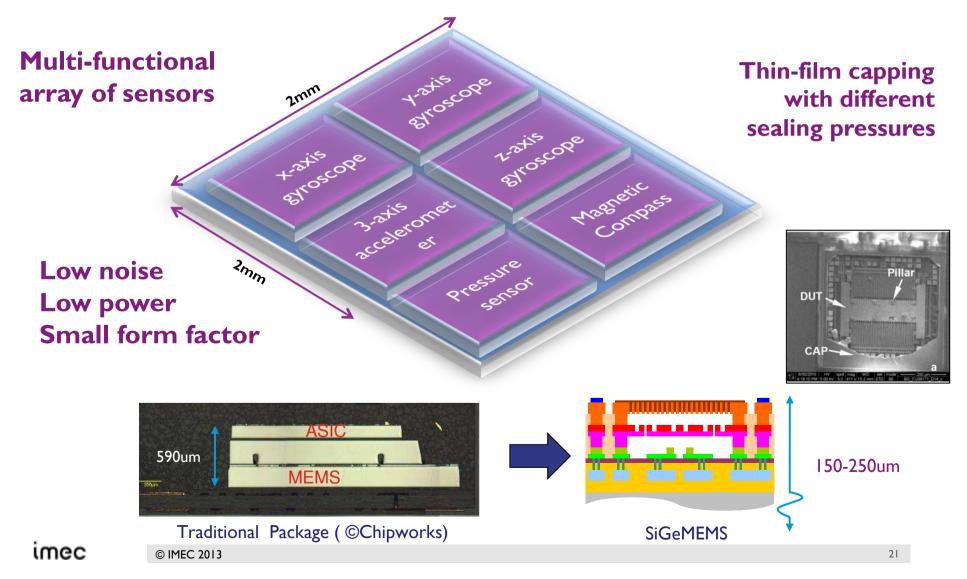

- Most MEMS devices are single components integrated with separate driver IC chip in multichip package.

- MEMS technologies are driven towards tighter integration with electronics for better performance, smaller form factors and packaging cost, enabled by:

- Above IC MEMS

- 3D Stacking

### CMORE SiGeMEMS TECHNOLOGY: I. MONOLITHIC INTEGRATION WITH IC

|                                            | 1. MOI                     |                                  |                                                  |                     |                                 | IEC<br>roach |

|--------------------------------------------|----------------------------|----------------------------------|--------------------------------------------------|---------------------|---------------------------------|--------------|

| Different MEMS-IC<br>ntegration approaches |                            | SIP: Stacked die<br>MEMS<br>CMOS | ABIC<br>ABIC<br>MORE<br>SIP: F2F<br>MEMS<br>CMOS | SIP: 3D vias        | SoC: monolithic<br>MEMS<br>CMOS |              |

|                                            | Interconnect<br>pitch      | ~ 50 um                          | ~I0um                                            | ~I0um               | ~lum                            |              |

|                                            | Interconnect<br>parasitics | few pF                           | >100fF                                           | <100fF              | few fF                          |              |

|                                            | yield                      | KGD                              | KGD<br>(unless W2W)                              | KGD<br>(unless W2W) | compound<br>yield               |              |

Monolithic approach:

- Most compact solution

- Better intrinsic system reliability: less components, less interconnections

- Best solution for applications that are very sensitive to parasitics

- BUT: MEMS yield is critical

### **CMORE SiGeMEMS TECHNOLOGY:** 2. MEMS LAST (ABOVE CMOS)

| Different Monolithic<br>MEMS approaches |                             |                           |                           |                                  | IMEC  |  |

|-----------------------------------------|-----------------------------|---------------------------|---------------------------|----------------------------------|-------|--|

|                                         |                             | ©SITime                   |                           | Appr                             | roach |  |

|                                         |                             | MEMS first                | intraCMOS                 | MEMS last                        |       |  |

|                                         |                             | MEMS                      | MEMS                      | MEMS                             |       |  |

|                                         | MEMS processing             | No thermal<br>limitations | T-budget<br>800°C         | T-budget<br>450°C                |       |  |

|                                         | CMOS                        | Non-standard              | Non-standard              | any standard<br>CMOS             |       |  |

|                                         | Interconnections<br>MEMS-IC | Peripheral<br>around MEMS | Peripheral<br>around MEMS | Distributed & massively parallel |       |  |

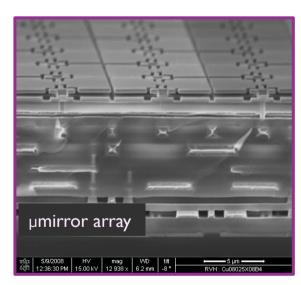

#### MEMS last:

- most flexible with respect to choice of CMOS technology

- very high-density and massively parallel interconnections possible

- $\rightarrow$  large arrays of MEMS (e.g. µmirror arrays)

- BUT: some loss in flexibility (e.g. material choice) due to T-budget

| CMORE SiGeMEMS TECHNOLOGY:                                     |                            |                               |           |             |  |

|----------------------------------------------------------------|----------------------------|-------------------------------|-----------|-------------|--|

| <b>3. POLY-SiGe</b><br>Different Above CMOS<br>MEMS approaches |                            | ©TI                           |           | EC<br>roach |  |

|                                                                |                            | AI                            | Poly-SiGe |             |  |

|                                                                | Post CMOS integration      | yes                           | yes       |             |  |

|                                                                | Fracture strength<br>[GPa] | 0.2                           | > 2       |             |  |

|                                                                | Mechanical Q               | low                           | > 10.000  |             |  |

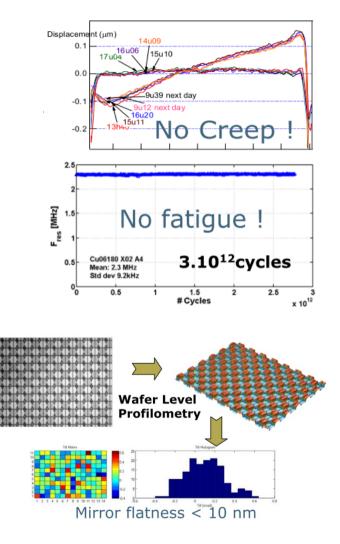

|                                                                | Reliability                | creep: hinge<br>memory effect | No creep  |             |  |

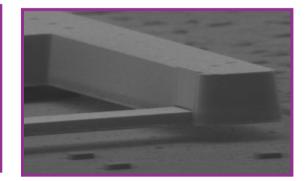

#### Poly-SiGe:

- better mechanical properties than AI: higher strength and Q factor

- better reliability properties than AI: less creep and fatigue

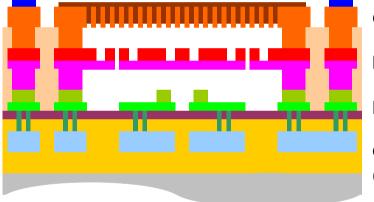

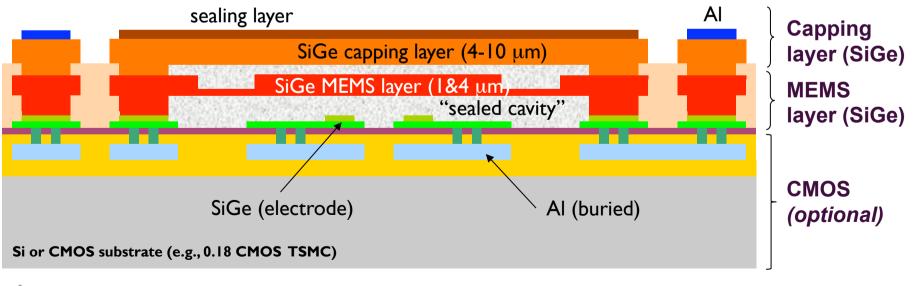

### **CMORE MEMS TECHNOLOGY FOCUS:** 4. FLEXIBLE & MODULAR TECHNOLOGY FLOW

| Monolithic               |

|--------------------------|

| Above-IC                 |

| SiGe-based               |

| Flexible MEMS technology |

|                          |

Capping & sealing layer

MEMS structural layer

Electrode layer

On top of "any" CMOS (on 200mm)

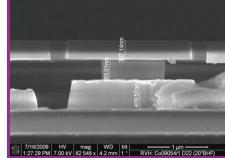

Surface micromachining on top of CMOS: temperature limited 450 °C for AI interconnections Poly-SiGe deposited at 450 °C E=140 GPa (60-70 *at.*% Ge) Stress = ~0-70 MPa Strain gradient =  $\pm 1 \times 10^{-5}/\mu$ m (4 µm thick CVD+PECVD SiGe) *Poly-Si*: 620 °C deposition, 800 °C needed for desired stress

Flexible and modular technology:

- Variable layer thicknesses

- Application-specific optimization of layer & material properties

- Application-specific functional add-on layers

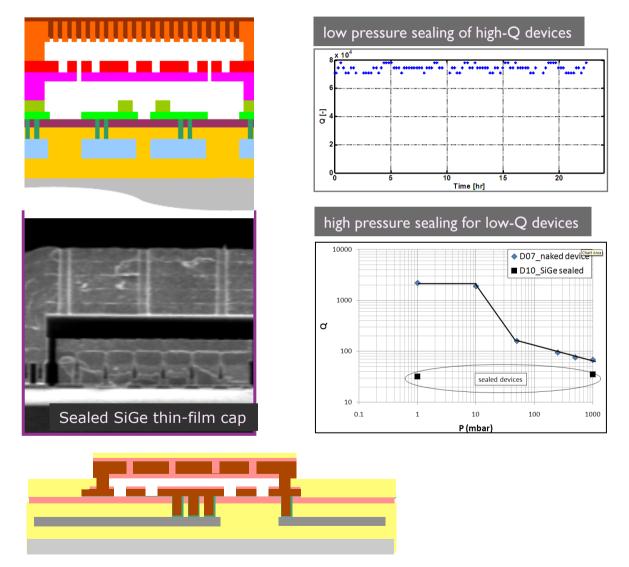

# Imec's SiGe MEMS – PLATFORM

Generic poly-SiGe technology for MEMS:

- "stand-alone" MEMS, or,

- "MEMS above IC" (CMOS-MEMS)

Two structural SiGe layers:

- MEMS structural layer (4μm standard)

- Thin film capping/packaging layer (4μm up to 10μm thick)

Gap in the SiGe structural layer:  $0.5\mu m$  (optional:  $0.2\mu m$ )

Low-T processing (< 460°C)

Hermetic package seal (I-100 Pa)

**Optional modules:**

- Optical (reflective)

- Electrical (metal trace)

- Piezo-resistive layer

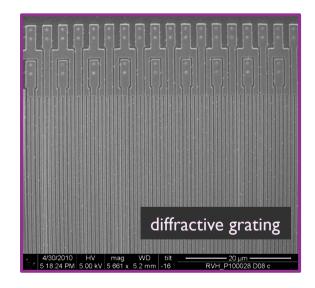

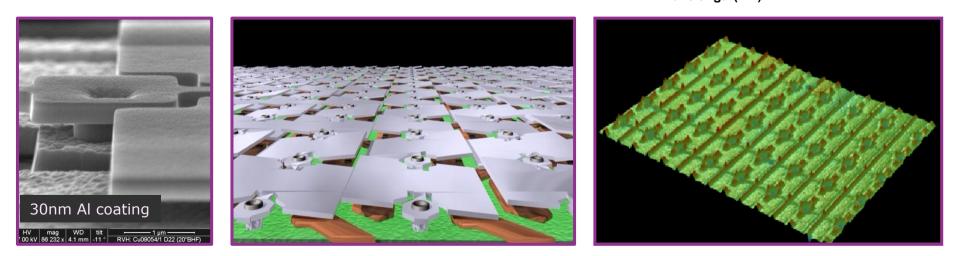

### FLEXIBILITY WITH LAYER THICKNESSES THIN STRUCTURAL LAYER

Thin SiGe platform

- structural layer thickness: 300nm

- gap: 200→50 nm

- actuation gap: 300 nm

- coating for optical properties

Thin SiGe layers

- stress: 20 MPa tensile

- strain gradient: le-4 / $\mu m$

- resistivity:  $Im\Omega cm$

Typical applications:

- µmirror arrays

- other optical MEMS: e.g. diffractive grating

© IMEC 2013

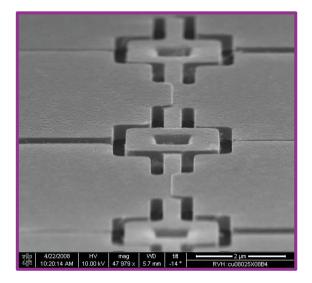

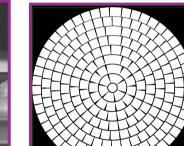

#### **EXPLOITING TECHNOLOGY FLEXIBILITY** FOR OPTIMIZED MICROMIRROR DESIGNS

Dual electrode thickness

- mechanical stopper

- reduce actuation voltage

Dual structural layer thicknessdecoupling spring constant and stiffness

Different µmirror design variants

- Analog vs digital tilt angles

- Circular vs rectangular arrays

- Single-axis vs two-axes mirrors

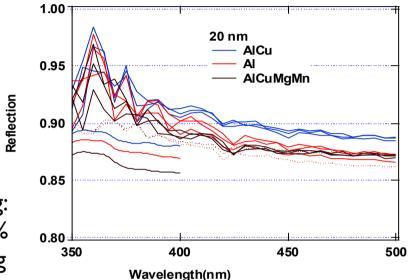

#### **MODULARITY VIA FUNCTIONAL LAYERS** OPTICAL REFLECTIVITY

Different coatings for optical MEMS:

- visual spectrum: 30nm AI coating

- IR applications: Ag coating

- (E)UV applications: Bragg stack

Al coating: • reflectivity > 85% • <5nm cupping

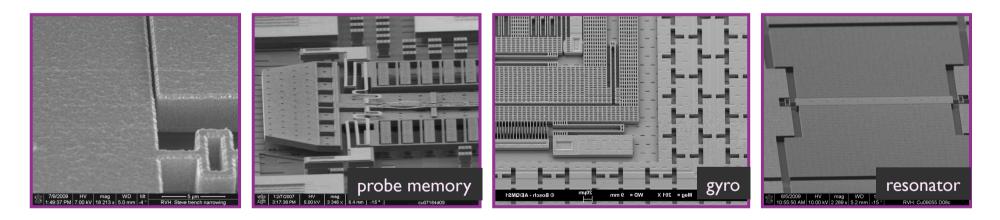

### FLEXIBILITY WITH LAYER THICKNESSES THICK STRUCTURAL LAYER

- "Plain-vanilla" thick SiGe platform

- structural layer thickness: 4µm

- nanogaps: 500→200 nm

Thick SiGe layers

- stress: 70 MPa tensile

- strain gradient: I e-5 / $\mu$ m

- resistivity:  $Im\Omega cm$

Typical applications:

- resonators, inertial sensors, actuators, ...

- probe-based memories

### MODULARITY VIA FUNCTIONAL LAYERS SEALING LAYER

SiGe membranes can be sealed:

• structural layer

• thin-film capping layer

Component applications:

• Capacitive Micromachined Ultrasound Transducers (CMUT)

• Pressure sensors

imec

© IMEC 2013

## **MEMS APPLICATIONS BUILD ON PLATFORM**

|                                 | Sensors            | Actuators    | Imaging &<br>Display | And many<br>other applications |

|---------------------------------|--------------------|--------------|----------------------|--------------------------------|

| Mechanical<br>functionality     | gyro               | switch       | µmirror array        | resonator probe memory         |

| Acoustic<br>functionality       | microphone         | loudspeaker  | CMUT                 |                                |

| Thermal<br>functionality        | T sensor           | micro heater | bolometer            | Thermal µpower                 |

| Bio / chemical<br>functionality | mass / gas sensing | Hactuator    |                      | ufluidics                      |

| •••                             |                    |              |                      |                                |

| C IMEC 2013                     |                    |              |                      | 17                             |

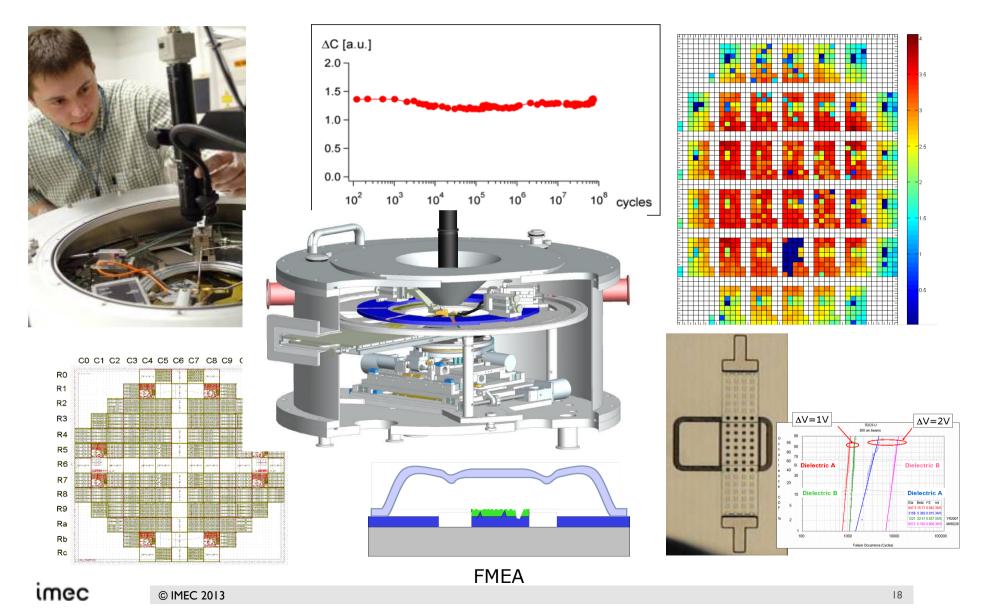

#### STRONG BACKGROUND IN MEMS CHARACTERIZATION AND RELIABILITY

## **CONCLUSIONS** IMEC SIGE MEMS TECHNOLOGY

#### Monolithic integration with IC

- Very compact & low cost

- Allows for higher performance

- Smaller footprint

#### SiGe-based above CMOS processing

- High performance: low parasitics

- Good mechanical properties & reliability

- Extremely well suited for MEMS array applications

#### Flexible and Modular

- Application-specific tuning and optimization

- Very versatile

### **IMEC (TECHNOLOGY) DIFFERENTIATORS**

- Support analog tilting of mirrors

- Produce micromirros with reliable performance

- SiGe mirrors are better material in terms of flexibility than AI (TI umirrors)  $\rightarrow$

- No creep

- No fatigue

- Flat mirror profiles

- Produce umirrors with higher performance

- Smaller mirrors (8umx8um demonstrated)

- large array sizes (> 10cm2)

- Large number of mirrors ~ IIM

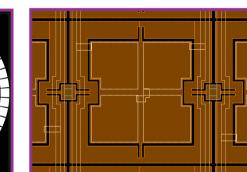

- Produce CMOS integrated umirror array

- Efficient integration of electronic control

- Efficient control of mirrors

### SiGeMEMS ALLOWS FOR MONOLITHIC INTEGRATION OF 10+ DEGREES-OF-FREEDOM INERTIAL MEASUREMENT UNIT

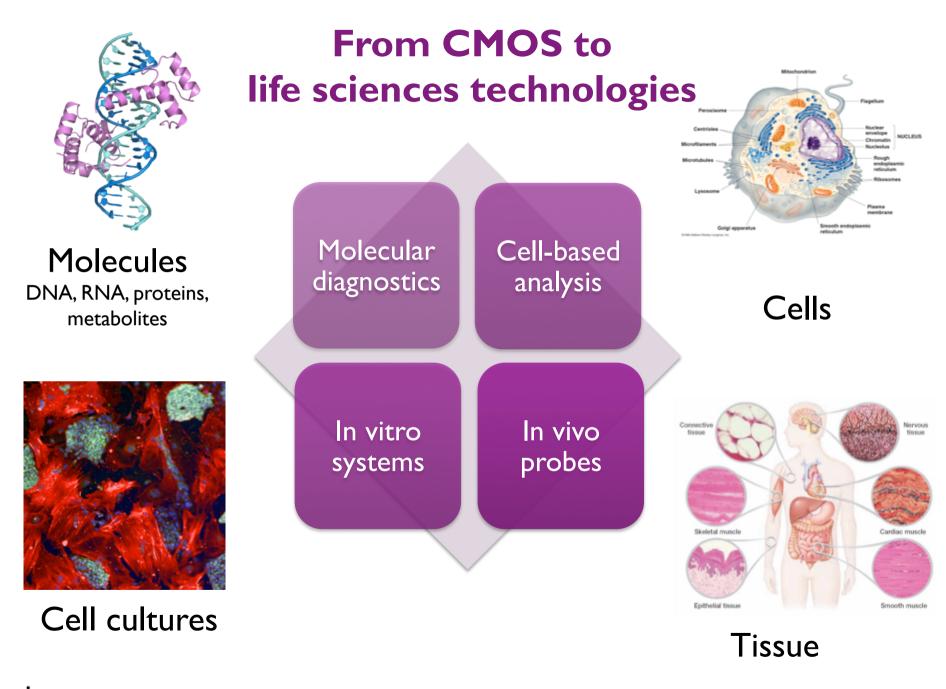

## FROM CMOS TO LIFE SCIENCES TECHNOLOGY

#### **Multidisciplinary teams**

Concept development

Process integration Process technology Fab operations

Cell biology Molecular biology Surface chemistry Assay development

imec © IMEC 2013

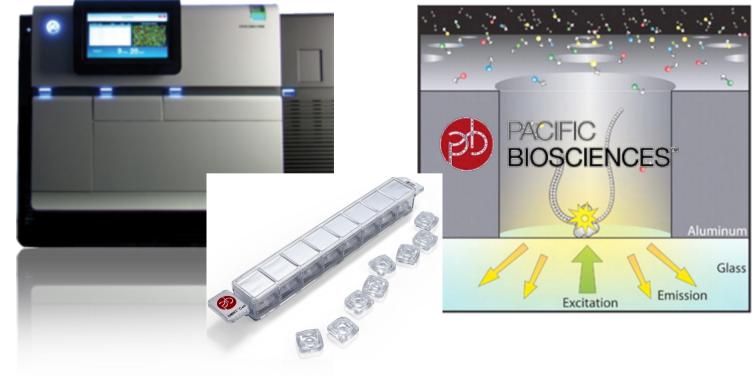

## **NEXT GENERATION SEQUENCING CHIPS**

July 23, 2012

#### Pacific Biosciences and Imec Announce Collaboration to Develop Advanced Microchips for Single Molecule Sequencing Applications

MENLO PARK, Calif., and LEUVEN, Belgium--(BUSINESS WIRE)-- Pacific Biosciences of California, Inc. (NASDAQ:PACB) provider of the PacBio<sup>®</sup> RS High Resolution Genetic Analyzer and Belgium-based nanoelectronics research center imec today announced a multi-year research collaboration focused on the development of advanced microchips for highly multiplexed single molecule genetic analysis. This research and development project will build on Pacific Biosciences' proprietary zero-mode waveguide (ZMW) technology and imec's world-leading expertise in nanophotonics, CMOS sensors, technology integration and fabrication.

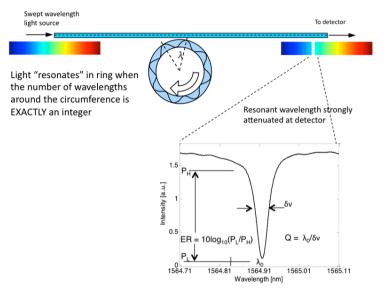

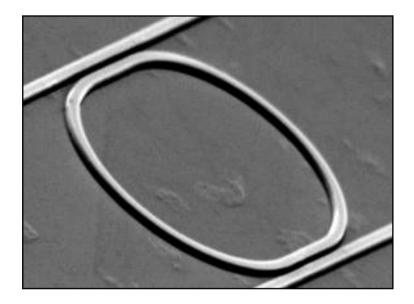

### **GENALYTE BIOSENSOR** SILICON PHOTONICS

source www.genalyte.com

Genalyte leverages imec silicon photonics platform to develop and manufacture (low-volume production) its disposable bio-sensor chips.

# **CELL BASED ANALYSIS**

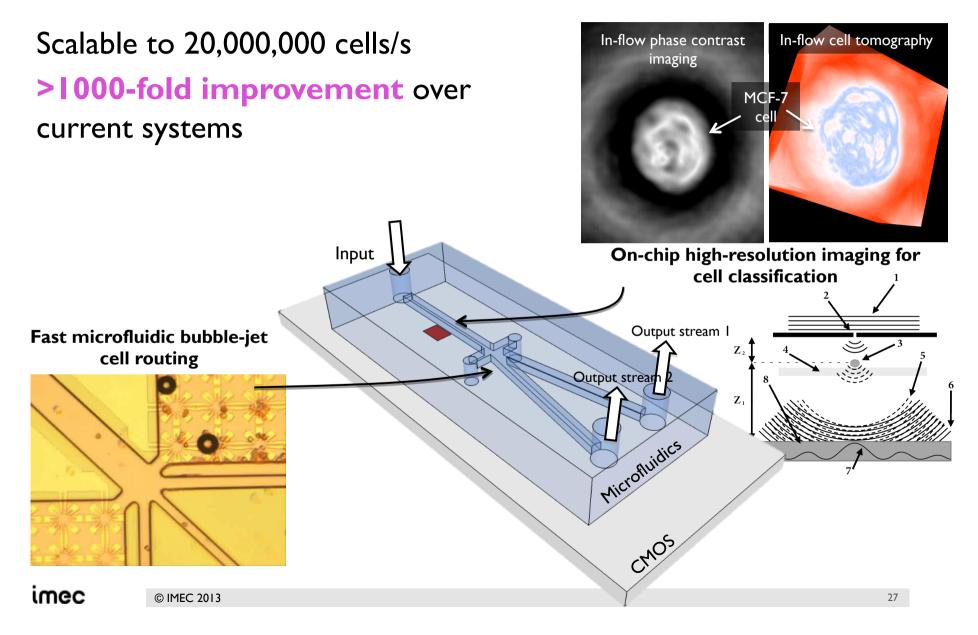

Finding individual cells is critical for cancer detection.

90% of cancer patients die from metastasis -- the cancer spreads via our circulation system

> I mL of blood contains: 10<sup>9</sup> blood cells

> > I Circulating Tumor Cell

#1 predictor of cancer survival is how early it's detected

## HIGH-THROUGHPUT IMAGING FLOW CYTOMETER

## FROM CMOS TO CMORE PLATFORM

imec